#### **OVERVIEW**

The MPEG-2 Decoder Core is a high performance and high quality solution video decompression engine targeted primarily at FPGAs. It is compliant with ISO/IEC 13818-2 (H.262) standards.

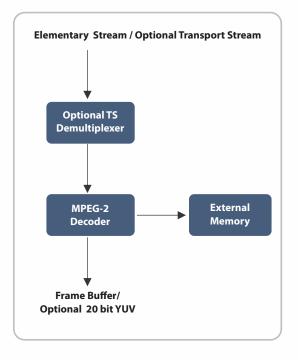

The decoder design is fully autonomous and does not require any external processor to aid the decode operation. The IO interface comprises of an input FIFO and an output frame buffer. Decoded data can also be provided on a serial bus with embedded sync information. The decoder requires single external DDR SDRAM to store reference pictures.

The decoder solution is available either as a FPGA netlist or in source code format and can be customized to meet the requirements of end users.

#### **KEY FEATURES**

- Fully standards compliant tested with ITU-T & other industry standard test suites

- · Robust error handling, resilience & concealment.

- Processes metadata related to closed captions & AFD.

- Seamless switching between streams encoded with different settings including different resolutions, chroma formats and bit depths

- · Single chip solution with no processor requirement

- Supports progressive and interlaced formats

- Easy to integrate and hence faster time-to-market

- · Low resource utilization

### **FPGA RESOURCES**

| FPGA              | LUTs  | BRAMs | DSPs |

|-------------------|-------|-------|------|

| Kintex Ultrascale | 9,000 | 42.5  | 65   |

- 1920 x 1080p60, 422, 8-bit, 100 mbps decoder

- Does not include memory controller, display controller and TS demultiplexer

# **BLOCK DIAGRAM**

#### **SPECIFICATIONS**

Standard: ISO/IEC 13818-2 (H.262)

Profiles: Simple, Main and 4:2:2

Video Resolutions: Up to 1920 x 1080

Frame Rate: Up to 60 fps

Bit rate: Up to 60 fps

100Mbps

**Chroma Format:** Monochrome, 4:2:0 & 4:2:2

**Precision:** 8 bits

**Input Format:** Elementary or Transport stream

Output Format: Decoded pictures in frame buffer. Optional serial

output with embedded sync information

**FPGA:** Xilinx Kintex Ultrascale, Kintex-7, Artix-7, Virtex-6 and

Spartan-6.

Altera devices are also supported. Contact us for

the information.

# **DELIVERABLES**

- Source Code or Netlist

- Simulation Model

- Hardware Test Platform

- Build Scripts

- Test Reports

- User Manual

- Design Documentation

- Constraint Files

- Test Benches

- Support for one year

# **APPLICATIONS**

BROADCAST

HIGH END CONSUMER ELECTRONICS

**TEST & MEASUREMENT EQUIPMENTS**

VIDEO / PLAYOUT SERVERS

AEROSPACE AND DEFENSE

MEDICAL

# VYUSYNC

VYUsync develops high performance video processing intellectual property cores. Our products cover a broad range of standards and are optimized for deployment across a wide array of segments including Contribution, Production, Distribution, Medical and Defense. VYUsync also develops hardware modules which incorporate the IP cores in order to allow our customers to reach market faster.