**RONIN** dynamic. powerful. robust.

## **OVERVIEW**

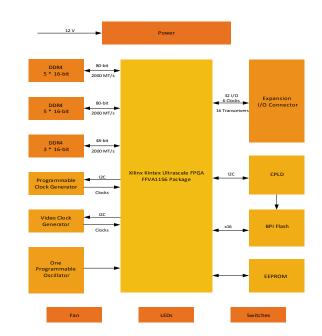

Ronin is multi codec video processing card designed to handle the rigorous requirements of modern video codecs. At the heart of the card is Xilinx Kintex Ultrascale FPGA. Three banks of DDR4 memory provide memory storage and bandwidth for processing compressed and baseband UHDp60 video. One expansion connector can be populated with daughter cards that enable audio processing and provide interfaces such as ASI, 12G SDI or 10-G Ethernet. The card is designed such that when decoding compressed content the FPGA can identify the video format employed and reconfigure itself to match the input format.

# **FEATURES**

| Xilinx Kintex Ultrascale - XCKU040-1TFFVA1156<br>Bank 1:80-bit wide 2.5 Gbyte DDR4 at 1GHz<br>[5x16 components each of 4Gb density]<br>Bank 2:80-bit wide 2.5 Gbyte DDR4 at 1GHz<br>[5x16 components each of 4Gb density]<br>Bank 3:48-bit wide 2.5 Gbyte DDR4 at 1GHz<br>[3x16 components each of 4Gb density]<br>One Programmable Oscillator<br>Video clock generator with 27 MHz, 148.5 and |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5x16 components each of 4Gb density]<br>Bank 2:80-bit wide 2.5 Gbyte DDR4 at 1GHz<br>[5x16 components each of 4Gb density]<br>Bank 3:48-bit wide 2.5 Gbyte DDR4 at 1GHz<br>[3x16 components each of 4Gb density]<br>One Programmable Oscillator                                                                                                                                               |

| [5x16 components each of 4Gb density]<br>Bank 3:48-bit wide 2.5 Gbyte DDR4 at 1GHz<br>[3x16 components each of 4Gb density]<br>One Programmable Oscillator                                                                                                                                                                                                                                     |

| [3x16 components each of 4Gb density]<br>One Programmable Oscillator                                                                                                                                                                                                                                                                                                                           |

| -                                                                                                                                                                                                                                                                                                                                                                                              |

| Video clock generator with 27 MHz, 148.5 and                                                                                                                                                                                                                                                                                                                                                   |

| 148.35 MHz clocks27 MHz clock is connected<br>I/O band 148.<br>148.5 and 148.35 MHz clocks are connected to GTX                                                                                                                                                                                                                                                                                |

| 3-PLL 3 output programmable clock generator<br>for DDR4 Controller                                                                                                                                                                                                                                                                                                                             |

| 1 GByte x16BPI flash                                                                                                                                                                                                                                                                                                                                                                           |

| Configuration control from FPGA, on board switched or expansion connectors                                                                                                                                                                                                                                                                                                                     |

| Expansion I/O Connector<br>[Samtec Z-Ray Interposer]<br>32 I/O<br>6 clocks<br>16 I/O Gigabit transceivers.8 I/O's out of 16,<br>can support PCle Gen 3                                                                                                                                                                                                                                         |

| 12 V 5A                                                                                                                                                                                                                                                                                                                                                                                        |

| Input Provision for up to 40 A for FPGA                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                |

### **VIDEO CORES SUPPORTED**

### Decoding

- MPEG-2 422 8 -bit 8 channels of HDp60

- AVC 422 10 -bit 4 channels of HDp60 or 1 channel of 4Kp60

- HEVC 422 12 -bit 4 channels of HDp60 or 1 channel of 4Kp60

- HEVC 444 12 -bit 2 channels of HDp60 or 1 channel of 4Kp30

#### Encoding

AVC Intra Frame 422 10 - bit - 4 channels of HDp60 or 1 channel of 4Kp60

#### **HARDWARE VIEW**

#### **BLOCK DIAGRAM**

# **RELATED OFFERINGS** -

#### Hardware

Schematics, PCB Layout, BOM

#### FPGA IP (source code or netlist)

- MPEG-2 Decoder FPGA IP core

- AVC Decoder FPGA IP core

- AVC Intra Frame Encoder FPGA IP core

- HEVC Decoder FPGA IP Core

# VYUSYNC

VVYUsync develops high performance video processing intellectual property cores. Our products cover a broad range of standards and are optimized for deployment across a wide array of segments including Contribution, Production, Distribution, Medical and Defense. VYUsync also develops hardware modules which incorporate the IP cores in order to allow our customers to reach market faster.

#### www.vyusync.com | contact@vyusync.com